# **I2S/TDM Library**

A software library that allows you to control an I<sup>2</sup>S or TDM (time division multiplexed) bus via xCORE ports. I<sup>2</sup>S and TDM are digital data streaming interface particularly appropriate for transmission of audio data. The components in the libary are controlled via C using the XMOS multicore extensions (xC) and can either act as I<sup>2</sup>S master, TDM master or I<sup>2</sup>S slave.

#### Features

- I<sup>2</sup>S master (sample and frame-based), TDM master and I<sup>2</sup>S slave modes.

- Handles multiple input and output data lines.

- Support for standard I<sup>2</sup>S, left justified or right justified data modes for I<sup>2</sup>S.

- Support for multiple formats of TDM synchronization signal.

- Sample rate support up to 192KHz.

- Up to 32 channels in/32 channels out (depending on sample rate)

#### Resource Usage

This following table shows typical resource usage in some different configurations. Exact resource usage will depend on the particular use of the library by the application.

| Configuration               | Pins           | Ports                       | Clocks | Ram   | Logical cores |

|-----------------------------|----------------|-----------------------------|--------|-------|---------------|

| I2S Master                  | 3 + data lines | 3 x (1-bit) +<br>data lines | 2      | ~2.1K | 1             |

| I2S Master<br>(frame-based) | 3 + data lines | 3 x (1-bit) +<br>data lines | 2      | ~1.6K | 1             |

| I2S Slave                   | 2 + data lines | 2 x (1-bit) +<br>data lines | 1      | ~1.5K | 1             |

| TDM Master                  | 2 + data lines | 2 x (1-bit) +<br>data lines | 1      | ~1.8K | 1             |

#### Software version and dependencies

This document pertains to version 2.2.0 of this library. It is known to work on version 14.2.3 of the xTIMEcomposer tools suite, it may work on other versions.

This library depends on the following other libraries:

• lib\_xassert (>=3.0.0)

• lib\_logging (>=2.1.0)

### **Related application notes**

The following application notes use this library:

• AN00162 - Using the I<sup>2</sup>S library

# 1 External signal description

# 1.1 I<sup>2</sup>S

$I^2S$  is a protocol between two devices where one is the *master* and one is the *slave*. The protocol is made up of four signals shown in Table 1.

| MCLK            | Clock line, driven by external oscillator                                                                                                    |  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|

| BCLK            | Bit clock. This is a fixed divide of the MCLK and is driven by the master.                                                                   |  |

| LRCLK (or WCLK) | Word clock (or word select). This is driven by the master.                                                                                   |  |

| DATA            | Data line, driven by one of the slave or master depending on the data direction.<br>There may be several data lines in differing directions. |  |

Table 1: I<sup>2</sup>S data wires

The configuration of an  $I^2S$  signal depends on the parameters shown in Table 2.

| MCLK_BCLK_RATIO | The fixed ratio between the master clock and the bit clock. |

|-----------------|-------------------------------------------------------------|

| MODE            | The mode - either I <sup>2</sup> S or left justified.       |

Table 2: I<sup>2</sup>S configuration parameters

The *MCLK\_BCLK\_RATIO* should be such that 64 bits can be output by the bit clock at the data rate of the I<sup>2</sup>S signal. For example, a 24.576MHz master clock with a ratio of 8 gives a bit clock at 3.072MHz. This bit clock can output 64 bits at a frequency of 48Khz - which is the underlying rate of the data.

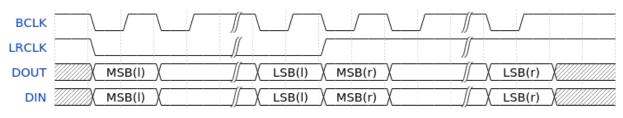

The master signals data transfer should occur by a transition on the *LRCLK* wire. There are two supported modes for  $I^2S$ . In *I2S mode* (shown in Figure 1) data is transferred on the second falling edge after the *LRCLK* transitions.

| BCLK        |                                                                          |

|-------------|--------------------------------------------------------------------------|

|             |                                                                          |

| DOUT MSB(I) | // X_LSB(I) X_MSB(r) X // X_LSB(r) X//////////////////////////////////// |

| DIN MSB(I)  | // X_LSB(I) X_MSB(r) X // X_LSB(r) X//////////////////////////////////// |

Figure 1: I<sup>2</sup>S Mode

In *Left Justified Mode* (shown in Figure 2) the data is transferred on the next falling edge after the *LRCLK* transition.

Figure 2: Left Justified Mode

In either case the signal multiplexes two channels of data onto one data line. When the *LRCLK* is low, the *left* channel is transmitted. When the *LRCLK* is high, the *right* channel is transmitted.

All data is transmitted most significant bit first. The xCORE I<sup>2</sup>S library assumes 32 bits of data between *LRCLK* transitions. How the data is aligned is expeced to be done in software by the application. For example, some audio codecs have a *Right Justified* mode; to attain this mode the library should be set to *Left Justified* mode to align the *LRCLK* signal and then the data should be right shifted by the application before being passed to the library.

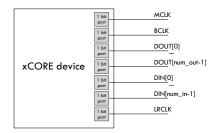

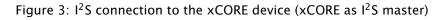

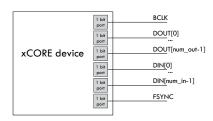

#### 1.1.1 Connecting I<sup>2</sup>S signals to the xCORE device

The  $I^2S$  wires need to be connected to the xCORE device as shown in Figure 3 and Figure 4. The signals can be connected to any one bit ports on the device provide they do not overlap any other used ports and are all on the same tile.

Figure 4: I<sup>2</sup>S connection to the xCORE device (xCORE as I<sup>2</sup>S slave)

If only one data direction is required then the *DOUT* or *DIN* lines need not be connected.

#### 1.1.2 I<sup>2</sup>S master speeds and performance

The speed and number of data wires that can be driven by the  $I^2S$  library running as  $I^2S$  master depends on the speed of the logical core that runs the code and the amount of processing that occurs in the user callbacks for handling the data from the library. Table 3 and Table 4 show configurations that are known to work for small amounts of callback processing. Other speeds will be achievable depending on the amount of processing in the application and the logical core speed.

| MCLK FREQ | MCLK/BCLK<br>RATIO | SAMPLE FREQ | NUM IN (num<br>channels) | NUM OUT (num channels) |

|-----------|--------------------|-------------|--------------------------|------------------------|

| 24.576MHz | 2                  | 192000      | 1 (2)                    | 1 (2)                  |

| 24.576MHz | 4                  | 96000       | 2 (4)                    | 2 (4)                  |

| 24.576MHz | 8                  | 48000       | 4 (8)                    | 4 (8)                  |

| 12.288MHz | 2                  | 96000       | 2 (4)                    | 2 (4)                  |

| 12.288MHz | 4                  | 48000       | 4 (8)                    | 4 (8)                  |

Table 3: Known working I<sup>2</sup>S master configurations on a 62.5MHz core

| MCLK FREQ | MCLK/BCLK<br>RATIO | SAMPLE FREQ | NUM IN (num<br>channels) | NUM OUT (num channels) |

|-----------|--------------------|-------------|--------------------------|------------------------|

| 24.576MHz | 2                  | 192000      | 2 (4)                    | 2 (4)                  |

| 24.576MHz | 4                  | 96000       | 4 (8)                    | 4 (8)                  |

| 12.288MHz | 2                  | 96000       | 4 (8)                    | 4 (8)                  |

Table 4: Known working I<sup>2</sup>S master configurations on a 83.3MHz core

On the xCORE-200 the frame-based  $I^2S$  master can be used. This uses hardware clock dividers only available in the the xCORE-200 and a more efficient callback interface to achieve much higher throughputs. Table 5 shows the known working configurations:

| MCLK FREQ | MCLK/BCLK<br>RATIO | SAMPLE FREQ | NUM IN (num<br>channels) | NUM OUT (num<br>channels) |

|-----------|--------------------|-------------|--------------------------|---------------------------|

| 24.576MHz | 2                  | 192000      | 4 (8)                    | 4 (8)                     |

Table 5: Known working I<sup>2</sup>S frame-based master configurations on a 62.5MHz core

#### 1.1.3 I<sup>2</sup>S slave speeds and performance

The speed and number of data wires that can be driven by the I<sup>2</sup>S library running as slave depends on the speed of the logical core that runs the code and the amount of processing that occurs in the user callbacks for handling the data from the library. Table 6 shows configurations that are known to work for small amounts of callback processing. Other speeds will be achievable depending on the amount of processing in the application and the logical core speed. Note that the when acting as slave the performance of the library only depends on the bit clock frequency, not the underlying master clock frequency.

| BCLK FREQU | SAMPLE FREQ | NUM IN (num channels) | NUM OUT (num channels) |

|------------|-------------|-----------------------|------------------------|

| 12.288MHz  | 192000      | 4 (8)                 | 4 (8)                  |

Table 6: Known working I<sup>2</sup>S slave configurations on a 62.5MHz core

# 1.2 TDM

TDM is a protocol that multiplexes several signals onto one wire. It is a protocol between two devices where one is the *master* and one is the *slave*. The protocol is made up of three signals shown in Table 7.

| BCLK  | Bit clock line, driven by external oscillator.                                                                                            |  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------|--|

| FSYNC | The frame sync line. This is driven by the master.                                                                                        |  |

| DATA  | Data line, driven by one of the slave or master depending on the data direction. There may be several data lines in differing directions. |  |

Table 7: TDM data wires

Unlike I<sup>2</sup>S, the bit clock is not a divide of an underlying master clock.

The configuration of a TDM signal depends on the parameters shown in Table 8.

| CHANNELS_PER_FRAME | The number of channels multiplexed into a frame on the data line.                                     |

|--------------------|-------------------------------------------------------------------------------------------------------|

| FSYNC_OFFSET       | The number of bits between the frame sync signal transitioning and data being drive on the data line. |

| FSYNC_LENGTH       | The number of bits that the frame sync signal stays high for when signalling frame start.             |

Table 8: TDM configuration parameters

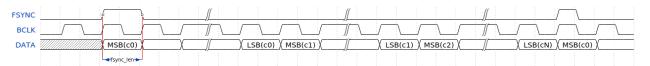

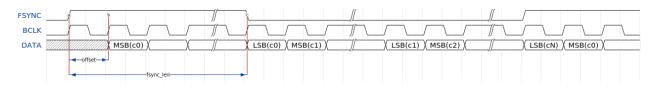

Figure 5 and Figure 6 show example waveforms for TDM with different offset and sync length values.

Figure 5: TDM signal (sync offset 0, sync length 1)

Figure 6: TDM signal (sync offset 1, sync length 32)

The master signals a frame by driving the *FSYNC* signal high. After a delay of *FSYNC\_OFFSET* bits, data is driven. Data is driven most significant bit first. First, 32 bits of data from Channel 0 is driven, then 32 bits from channel 1 up to channel N (when N is the number of channels per frame). The next frame is then signalled (there is no padding between frames).

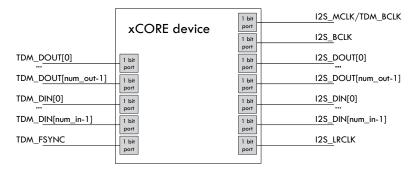

#### 1.2.1 Connecting TDM signals to the xCORE device

The TDM wires need to be connected to the xCORE device as shown in Figure 7. The signals can be connected to any one bit ports on the device provide they do not overlap any other used ports and are all on the same tile.

Figure 7: TDM connection to the xCORE device

If only one data direction is required then the DOUT or DIN lines need not be connected.

#### 1.2.2 TDM speeds and performance

The speed and number of data wires that can be driven by the I<sup>2</sup>S library running as TDM master depends on the speed of the logical core that runs the code and the amount of processing that occurs in the user callbacks for handling the data from the library. Table 9 show configurations that are known to work for small amounts of callback processing. Other speeds will be achievable depending on the amount of processing in the application and the logical core speed.

| BCLK FREQ | CHANNELS PER<br>FRAME | SAMPLE FREQ | NUM IN (num<br>channels) | NUM OUT (num channels) |

|-----------|-----------------------|-------------|--------------------------|------------------------|

| 12.288MHz | 8                     | 48000       | 2 (16)                   | 2 (16)                 |

| 6.144MHz  | 4                     | 48000       | 4 (16)                   | 4 (16)                 |

Table 9: Known working TDM configurations on a 62.5MHz core

# 1.3 Combined I<sup>2</sup>S and TDM

The library can drive synchronized  $I^2S$  master and TDM signals from a single logical core. In this case, the *MCLK* of the  $I^2S$  interface is the same as the *BCLK* of the TDM master. The sample rate must be the same. This implies that the TDM channels per frame must be equal to the twice the *MCLK/BCLK* ratio.

#### 1.3.1 Connecting synchronized I<sup>2</sup>S and TDM signals to the xCORE device

The  $I^2S$  and TDM wires need to be connected to the xCORE device as shown in Figure 8. The signals can be connected to any one bit ports on the device provide they do not overlap any other used ports and are all on the same tile.

Figure 8:  $I^2S$  + TDM connection to the xCORE device

If only one data direction is required then the DOUT or DIN lines need not be connected.

#### 1.3.2 Combined I<sup>2</sup>S and TDM speeds and performance

The speed and number of data wires that can be driven by the library running combined I<sup>2</sup>S master and TDM depends on the speed of the logical core that runs the code and the amount of processing that occurs in the user callbacks for handling the data from the library. Table 10 show configurations that are known to work for small amounts of callback processing. Other speeds will be achievable depending on the amount of processing in the application and the logical core speed.

| MCLK FREQ | MCLK/BCLK<br>RATIO | SAMPLE FREQ | CHANNELS<br>PER TDM<br>FRAME | I2S IN/OUT<br>(channels<br>in/out) | TDM IN/OUT<br>(channels in-<br>/out) |

|-----------|--------------------|-------------|------------------------------|------------------------------------|--------------------------------------|

| 12.288MHz | 4                  | 48000       | 8                            | 4/4 (8/8)                          | 1/1 (8/8)                            |

Table 10: Known working  $I^2S$  + TDM configurations on a 62.5MHz core

# 2 Usage

All I<sup>2</sup>S functions can be accessed via the i2s.h header:

```

#include <i2s.h>

```

You will also have to add lib\_i2s to the USED\_MODULES field of your application Makefile.

# 2.1 The I<sup>2</sup>S callback interface

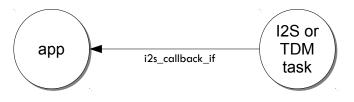

All major functions in the  $I^2S$  library work by controlling the  $I^2S$  or TDM bus on its own logical core on an xCORE device. The library will then make callbacks to the application when it receives a sample or needs to send a sample.

Figure 9: I<sup>2</sup>S callback usage

The callbacks are implemented by the application providing a task which receives requests on the i2s\_callback\_if xC interface. The application tasks can run the callbacks on the same logical core by implementing a *distributable* task. More information on interfaces and tasks can be be found in the XMOS Programming Guide (see XM-004440-PC).

A template application task is shown below. The specific contents of each callback will depend on the application:

```

[[distributable]]

void my_application(server i2s_callback_if i2s) {

while (1) {

select {

case i2s.init(i2s_config_t &?i2s_config, tdm_config_t &?tdm_config):

i2s_config.mclk_to_bclk_ratio = 2;

i2c_config.mode = I2S_MODE_LEFT_JUSTIFIED;

. . .

break;

case i2s.restart_check() -> i2s_restart_t restart:

break;

case i2s.receive(size_t index, int32_t sample):

break;

case i2s.send(size_t index) -> int32_t sample:

break;

}

}

```

The send/receive callbacks pass a channel index parameter to the application. This channel maps to the

data signals as shown in §2.7.

The initialization callback will provide configuration structures relevant to the communication bus being used. The application can set the parameters of the bus (*MCLK/BCLK* ratio, *LRCLK* alignment etc.) at this point.

# 2.2 I<sup>2</sup>S master usage

The I<sup>2</sup>S master task is instantiated as a parallel task that run in a par statement. The application can connect via the i2s\_callback\_if interface connection. For example, the following code instantiates an I<sup>2</sup>S master component and connects to it:

```

out buffered port:32 p_dout[2] = {XS1_PORT_1D, XS1_PORT_1E};

in buffered port:32 p_din[2] = {XS1_PORT_1I, XS1_PORT_1K};

port p_mclk = XS1_PORT_1M;

out buffered port:32 p_bclk = XS1_PORT_1A;

out buffered port:32 p_lrclk = XS1_PORT_1C;

clock mclk = XS1_CLKBLK_1;

clock bclk = XS1_CLKBLK_2;

int main(void) {

i2s_callback_if i_i2s;

configure_clock_src(mclk, p_mclk);

start_clock(mclk);

par {

i2s_master(i_i2s, p_dout, 2, p_din, 2,

p_bclk, p_lrclk, bclk, mclk);

my_application(i_i2s);

}

return 0;

}

```

# 2.3 I<sup>2</sup>S frame-based master usage

The I<sup>2</sup>S frame-based master task (only supported on xCORE-200) is instantiated as a parallel task that run in a par statement. The application can connect via the i2s\_frame\_callback\_if interface connection. For example, the following code instantiates an I<sup>2</sup>S frame-based master component and connects to it:

```

out buffered port:32 p_dout[2] = {XS1_PORT_1D, XS1_PORT_1E};

in buffered port:32 p_din[2] = {XS1_PORT_1I, XS1_PORT_1K};

port p_mclk = XS1_PORT_1M;

out buffered port:32 p_bclk = XS1_PORT_1A;

out buffered port:32 p_lrclk = XS1_PORT_1C;

clock mclk = XS1_CLKBLK_1;

clock bclk = XS1_CLKBLK_2;

int main(void) {

i2s_frame_callback_if i_i2s;

par {

i2s_frame_master(i_i2s, p_dout, 4, p_din, 4,

p_bclk, p_lrclk, p_mclk, bclk);

my_application(i_i2s);

}

return 0;

}

```

# 2.4 I<sup>2</sup>S slave usage

The  $I^2S$  slave task is instantiated as a parallel task that run in a par statement. The application can connect via the  $i2s_callback_if$  interface connection. For example, the following code instantiates an  $I^2S$  slave component and connects to it:

### 2.5 TDM usage

The TDM master task is instantiated as a parallel task that run in a par statement. The application can connect via the i2s\_callback\_if interface connection. For example, the following code instantiates an TDM master component and connects to it:

```

out buffered port:32 p_dout[2] = {XS1_PORT_1D, XS1_PORT_1E};

in buffered port:32 p_din[2] = {XS1_PORT_1I, XS1_PORT_1K};

in port p_bclk = XS1_PORT_1A;

out buffered port:32 p_fsync = XS1_PORT_1C;

clock bclk = XS1_CLKBLK_1;

int main(void) {

i2s_callback_if i_i2s;

configure_clock_src(bclk, p_bclk);

par {

tdm_master(i2s_i, p_fsync, p_dout, 2, p_din, 2, bclk);

my_application(i_i2s);

}

return 0;

}

```

# 2.6 I<sup>2</sup>S + TDM usage

You can run TDM and  $I^2S$  master on one core via a task that is instantiated in a par statement. The application can connect via the i2s\_callback\_if interface connection. For example, the following code instantiates an  $I^2S$  + TDM master component and connects to it:

```

out buffered port:32 p_i2s_dout[2] = {XS1_PORT_1B, XS1_PORT_1F};

in buffered port:32 p_i2s_din[2] = {XS1_PORT_1G, XS1_PORT_1H};

out buffered port:32 p_tdm_dout[1] = {XS1_PORT_1D};

in buffered port:32 p_tdm_din[1] = {XS1_PORT_1I};

in port p_mclk = XS1_PORT_1A;

out buffered port:32 p_fsync = XS1_PORT_1C;

out buffered port:32 p_bclk = XS1_PORT_1E;

out buffered port:32 p_lrclk = XS1_PORT_1K;

clock bclk = XS1_CLKBLK_1;

clock mclk = XS1_CLKBLK_2;

int main(void) {

i2s_callback_if i_i2s;

configure_clock_src(mclk, p_mclk);

start_clock(mclk);

par {

i2s_tdm_master(i2s_i, p_i2s_dout, 2, p_i2s_din, 2,

p_bclk, p_lrclk, p_fsync,

tdm_dout, 1, tdm_din, 1,

bclk, mclk);

my_application(i_i2s);

}

return 0;

}

```

# 2.7 Channel numbering

The callback interface numbers the channels being sent/received for the send and receive callbacks. There is a fixed mapping from these channel indices to the physical interface begin used.

#### Copyright 2016 XMOS Ltd.

#### 2.7.1 I<sup>2</sup>S channel numbering

The data words within I<sup>2</sup>S frames have even channel numbers assigned to the left samples (first within the frame) and odd numbers assigned to the right (second within the frame) samples.

The actual sample number will be given with respect to the order that the ports are provided in the data in and data out array arguments to the component.

For example, in a system with 4 data out ports and 4 data in ports declared as:

out buffered port:32 p\_dout[4] = {XS1\_PORT\_1A, XS1\_PORT\_1B, XS1\_PORT\_1C, XS1\_PORT\_1D}; in buffered port:32 p\_din[4] = {XS1\_PORT\_1E, XS1\_PORT\_1F, XS1\_PORT\_1G, XS1\_PORT\_1H};

LRCLK DOUT[0] 0 1 0 1 2 2 DOUT[1] 3 3 DOUT[2] 4 5 4 5 DOUT[3] 6 7 6 7 DIN[0] 0 1 0 1 DIN[1] 2 3 2 3 5 DIN[2] 4 5 4 DIN[3] 6 7 6 7

The channels wil be numbered as indicated in Figure 10:

Figure 10: I<sup>2</sup>S channel numbering

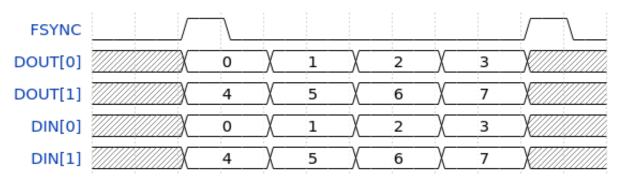

#### 2.7.2 TDM channel numbering

The data words within TDM frames are assigned sequentially from the start of the frame. Each data line will have its channel numbers assigned in the order that the ports are provided in the data in and data out array arguments to the component.

For example, in a system with 2 data out ports and 2 data in ports declared as:

out buffered port:32 p\_dout[2] = {XS1\_PORT\_1A, XS1\_PORT\_1B}; in buffered port:32 p\_din[2] = {XS1\_PORT\_1E, XS1\_PORT\_1F};

With the number of channels per frame as 4, the samples will be numbered as indicated in Figure 11:

Figure 11: TDM channel numbering

#### 2.7.3 I<sup>2</sup>S and TDM combined numbering

When using the I<sup>2</sup>S/TDM combined task the TDM channels are numbered after the I<sup>2</sup>S channels using the numbering system described in the previous two sections.

#### 2.8 Callback sequences

The send/receive callbacks of  $I^2S$  callbacks occur in a pre-determined order. The sequence consists of receipt of all even channel, sending of all even channels, receipt of all odd channels and then sending of all odd channels.

Since the hardware port buffers within the xCORE device there is an initial sequences of sends after initialization. Similarly there is a final sequences of receives after a restart/shutdown request. Table 11 shows an example sequence of callbacks for two output lines and two input lines (four channels in and four channels out).

| S0 S2 S1 S3             |

|-------------------------|

| R0 R2 S0 S2 R1 R3 S1 S3 |

| R0 R2 S0 S2 R1 R3 S1 S3 |

|                         |

| R0 R2 S0 S2 R1 R3 S1 S3 |

| R0 R2 R1 R3             |

|                         |

Table 11: Sample I<sup>2</sup>S callback sequence

When using TDM, the receive callbacks for a channel occur after the send callbacks. The receive callback for the last channel of the frame will occur after the send callback for the next frame. After a restart request a tail of receive callbacks for the last channel of the final frame will occur. Table 12 shows an example TDM callback sequence for two data lines in and out with four channels per frame.

S0 S4 S1 S5 R0 R4 S2 S6 R1 R5 S3 S7 R2 R6 S0 S4 R3 R7 S1 S5 R0 R4 S2 S6 R1 R5 S3 S7 R2 R6 ... S0 S4 R3 R7 S1 S5 R0 R4 S2 S6 R1 R5 S3 S7 R2 R6 S0 S4 R3 R7 S1 S5 R0 R4 S2 S6 R1 R5 S3 S7 R2 R6 R3 R7

Table 12: Sample TDM callback sequence

In both cases the components attempt to distribute the calling of the callbacks evenly within the frame to allow processing to occur throughout the frame evenly.

The restart\_check callback is called once per frame to allow the application to request a restart/shutdown of the data bus.

# 2.9 Clock configuration

For the  $I^2S$  master and TDM components is it the application's responsibility to set up and start the internal clock used for the master clock before calling the component.

For example, the following code configures a clock to be based of an incoming data wire and starts the clock:

```

configure_clock_src(mclk, p_mclk);

start_clock(mclk);

```

For more information on configuring clocks see the XMOS tools user guide.

# 3 API

# 3.1 Supporting types

| Туре        | i2s_mode_t                                                                   |

|-------------|------------------------------------------------------------------------------|

| Description | I2S mode.<br>This type is used to describe the I2S mode.                     |

| Values      | I2S_MODE_I2S<br>The LR clock transitions ahead of the data by one bit clock. |

|             | I2S_MODE_LEFT_JUSTIFIED<br>The LR clock and data are phase aligned.          |

| Туре        | i2s_config_t                                                                              |

|-------------|-------------------------------------------------------------------------------------------|

| Description | I2S configuration structure.<br>This structure describes the configuration of an I2S bus. |

| Fields      | unsigned mclk_bclk_ratio<br>The ratio between the master clock and bit clock signals.     |

|             | <pre>i2s_mode_t mode    The mode of the LR clock.</pre>                                   |

| Туре        | tdm_config_tTDM configuration structure.This structure describes the configuration of a TDM bus.                                                                                                                                                 |  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Description |                                                                                                                                                                                                                                                  |  |  |

| Fields      | <pre>int offset     The number of bits that the FSYNC signal transitions before the data.     Must be a value between -31 and 31. unsigned sync_len     The length that the FSYNC signal stays high counted as ticks of the bit     clock.</pre> |  |  |

|             | unsigned channels_per_frame<br>The number of channels in a TDM frame. This must be a power of 2.                                                                                                                                                 |  |  |

| Туре        | i2s_restart_t                                                                                                                                                             |  |  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Description | Restart command type.<br>Restart commands that can be signalled to the I2S or TDM component.                                                                              |  |  |

| Values      | I2S_NO_RESTART<br>Do not restart.<br>I2S_RESTART<br>Restart the bus (causes the I2S/TDM to stop and a new init callback to<br>occur allowing reconfiguration of the BUS). |  |  |

|             | I2S_SHUTDOWN<br>Shutdown. This will cause the I2S/TDM component to exit.                                                                                                  |  |  |

# 3.2 Creating an I<sup>2</sup>S instance

| Function    | i2s_master                                                                                                                                                                                                                                                                      | r                                                                                                                                                                                                                                                                   |  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Description | I2S master component.<br>This task performs I2S on the provided pins. It will perform callbacks of<br>i2s_callback_if interface to get/receive data from the application using this of<br>nent.<br>The component performs I2S master so will drive the word clock and bit clock |                                                                                                                                                                                                                                                                     |  |

| Туре        | out bu<br>static<br>in buf<br>static<br>out bu<br>out bu<br>clock                                                                                                                                                                                                               | <pre>r(client i2s_callback_if i2s_i,<br/>ffered port:32(&amp; ?p_dout)[num_out],<br/>const size_t num_out,<br/>fered port:32(&amp; ?p_din)[num_in],<br/>const size_t num_in,<br/>ffered port:32 p_bclk,<br/>ffered port:32 p_lrclk,<br/>bclk,<br/>clock mclk)</pre> |  |

| Parameters  | i2s_i                                                                                                                                                                                                                                                                           | The I2S callback interface to connect to the application                                                                                                                                                                                                            |  |

|             | p_dout                                                                                                                                                                                                                                                                          | An array of data output ports                                                                                                                                                                                                                                       |  |

|             | num_out                                                                                                                                                                                                                                                                         | The number of output data ports                                                                                                                                                                                                                                     |  |

|             | p_din                                                                                                                                                                                                                                                                           | An array of data input ports                                                                                                                                                                                                                                        |  |

|             | num_in                                                                                                                                                                                                                                                                          | The number of input data ports                                                                                                                                                                                                                                      |  |

|             | p_bclk                                                                                                                                                                                                                                                                          | The bit clock output port                                                                                                                                                                                                                                           |  |

|             | p_lrclk                                                                                                                                                                                                                                                                         | The word clock output port                                                                                                                                                                                                                                          |  |

|             | bclk                                                                                                                                                                                                                                                                            | A clock that will get configured for use with the bit clock                                                                                                                                                                                                         |  |

|             | mclk                                                                                                                                                                                                                                                                            | The clock connected to the master clock frequency. Usually this should be configured to be driven by an incoming master system clock.                                                                                                                               |  |

| Function    | i2s_frame_                                                                                                                                                                                                                                                                                                                                     | master                                                         |  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--|

| Description | I2S frame-based master component <b>for xCORE200 only</b> .<br>This task performs I2S on the provided pins. It will perform callbacks over the i2s_frame_callback_if interface to get/receive frames of data from the application using this component.<br>The component performs I2S master so will drive the word clock and bit clock lines. |                                                                |  |

| Туре        | <pre>void<br/>i2s_frame_master(client i2s_frame_callback_if i2s_i,<br/>out buffered port:32(&amp; ?p_dout)[num_out],<br/>static const size_t num_out,<br/>in buffered port:32(&amp; ?p_din)[num_in],<br/>static const size_t num_in,<br/>out port p_bclk,<br/>out buffered port:32 p_lrclk,<br/>in port p_mclk,<br/>clock bclk)</pre>          |                                                                |  |

| Parameters  | i2s_i                                                                                                                                                                                                                                                                                                                                          | The I2S frame callback interface to connect to the application |  |

|             | p_dout                                                                                                                                                                                                                                                                                                                                         | An array of data output ports                                  |  |

|             | num_out                                                                                                                                                                                                                                                                                                                                        | The number of output data ports                                |  |

|             | p_din                                                                                                                                                                                                                                                                                                                                          | An array of data input ports                                   |  |

|             | num_in                                                                                                                                                                                                                                                                                                                                         | The number of input data ports                                 |  |

|             | p_bclk                                                                                                                                                                                                                                                                                                                                         | The bit clock output port                                      |  |

|             | p_lrclk                                                                                                                                                                                                                                                                                                                                        | The word clock output port                                     |  |

|             | p_mclk                                                                                                                                                                                                                                                                                                                                         | Input port which supplies the master clock                     |  |

|             | bclk                                                                                                                                                                                                                                                                                                                                           | A clock that will get configured for use with the bit clock    |  |

| Function    | i2s_slave                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                    |  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Description | I2S slave component.<br>This task performs I2S on the provided pins. It will perform callbacks over the<br>i2s_callback_if interface to get/receive data from the application using this compo-<br>nent.<br>The component performs I2S slave so will expect the word clock and bit clock to be<br>driven externally. |                                                                                                                                                                                                                                    |  |

| Туре        | out buf<br>static<br>in buff<br>static<br>in port                                                                                                                                                                                                                                                                    | <pre>(client i2s_callback_if i2s_i,<br/>fered port:32(&amp; ?p_dout)[num_out],<br/>const size_t num_out,<br/>fered port:32(&amp; ?p_din)[num_in],<br/>const size_t num_in,<br/>cp_bclk,<br/>fered port:32 p_lrclk,<br/>oclk)</pre> |  |

| Parameters  | i2s_i                                                                                                                                                                                                                                                                                                                | The I2S callback interface to connect to the application                                                                                                                                                                           |  |

|             | p_dout                                                                                                                                                                                                                                                                                                               | An array of data output ports                                                                                                                                                                                                      |  |

|             | num_out                                                                                                                                                                                                                                                                                                              | The number of output data ports                                                                                                                                                                                                    |  |

|             | p_din                                                                                                                                                                                                                                                                                                                | An array of data input ports                                                                                                                                                                                                       |  |

|             | num_in                                                                                                                                                                                                                                                                                                               | The number of input data ports                                                                                                                                                                                                     |  |

|             | p_bclk                                                                                                                                                                                                                                                                                                               | The bit clock input port                                                                                                                                                                                                           |  |

|             | p_lrclk                                                                                                                                                                                                                                                                                                              | The word clock input port                                                                                                                                                                                                          |  |

|             | bclk                                                                                                                                                                                                                                                                                                                 | A clock that will get configured for use with the bit clock                                                                                                                                                                        |  |

# 3.3 Creating an TDM instance

| Function    | tdm_maste                                                                                                                                                                                                                                                                                   | er in the second s |  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Description | <ul> <li>TDM master component.</li> <li>This task performs TDM on the provided pins. It will perform callbacks i2s_callback_if interface to get/receive data from the application using this nent.</li> <li>The component performs as TDM master so will drive the fsync signal.</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| Туре        | <pre>void<br/>tdm_master(client interface i2s_callback_if tdm_i,<br/>out buffered port:32 p_fsync,<br/>out buffered port:32(&amp; ?p_dout)[num_out],<br/>size_t num_out,<br/>in buffered port:32(&amp; ?p_din)[num_in],<br/>size_t num_in,<br/>clock clk)</pre>                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| Parameters  | tdm_i                                                                                                                                                                                                                                                                                       | The TDM callback interface to connect to the application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|             | p_fsync                                                                                                                                                                                                                                                                                     | The frame sync output port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|             | p_dout                                                                                                                                                                                                                                                                                      | An array of data output ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|             | num_out                                                                                                                                                                                                                                                                                     | The number of output data ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|             | p_din                                                                                                                                                                                                                                                                                       | An array of data input ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|             | num_in                                                                                                                                                                                                                                                                                      | The number of input data ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|             | clk                                                                                                                                                                                                                                                                                         | The clock connected to the bit/master clock frequency. Usually this should be configured to be driven by an incoming master system clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| Function    | i2s_tdm_master                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Description | <ul> <li>I2S master + TDM master component.</li> <li>This task performs I2S and TDM on the provided pins. The signals need to be synchronized. It will perform callbacks over the i2s_callback_if interface to get/receive data from the application using this component.</li> <li>The component assumes that the bit clock of the TDM signal is the same as the master clock of the I2S signal.</li> <li>The component performs I2S master so will drive the word clock and bit clock lines. It will also acts as TDM master and drives the fsync signal.</li> </ul> |  |  |

| Туре        | <pre>void<br/>i2s_tdm_master(client interface i2s_callback_if tdm_i,<br/>out buffered port:32 i2s_dout[num_i2s_out],<br/>static const size_t num_i2s_out,<br/>in buffered port:32 i2s_din[num_i2s_in],<br/>static const size_t num_i2s_in,<br/>out buffered port:32 i2s_bclk,<br/>out buffered port:32 i2s_lrclk,<br/>out buffered port:32 tdm_fsync,<br/>out buffered port:32 tdm_dout[num_tdm_out],<br/>size_t num_tdm_out,<br/>in buffered port:32 tdm_din[num_tdm_in],<br/>size_t num_tdm_in,<br/>clock bclk,<br/>clock mclk)</pre>                                |  |  |

Continued on next page

| 2s_dout<br>um_i2s_out | An array of I2S data output ports                                                                                                                                                         |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| um_i2s_out            |                                                                                                                                                                                           |

|                       | The number of I2S output data ports                                                                                                                                                       |

| 2s_din                | An array of I2S data input ports                                                                                                                                                          |

| um_i2s_in             | The number of I2S input data ports                                                                                                                                                        |

| 2s_bclk               | The I2S bit clock output port                                                                                                                                                             |

| 2s_lrclk              | The I2S word clock output port                                                                                                                                                            |

| dm_fsync              | The TDM frame sync output port                                                                                                                                                            |

| dm_dout               | An array of TDM data output ports                                                                                                                                                         |

| um_tdm_out            | The number of TDM output data ports                                                                                                                                                       |

| dm_din                | An array of TDM data input ports                                                                                                                                                          |

| um_tdm_in             | The number of TDM input data ports                                                                                                                                                        |

| c1k                   | A clock that will get configured for use with the I2S bit clock                                                                                                                           |

|                       | The clock connected to the master clock frequency. Usually this should<br>be configured to be driven by an incoming master system clock. This<br>clock is also used as the TDM bit clock. |

|                       | 2s_din<br>um_i2s_in<br>2s_bclk<br>2s_lrclk<br>dm_fsync<br>dm_dout<br>um_tdm_out<br>dm_din<br>um_tdm_in<br>clk<br>clk                                                                      |

# 3.4 The I<sup>2</sup>S callback interface

| Туре        | i2s_callback_if                                                                            |                                                                                                                                                                               |

|-------------|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Description | Interface representing callback events that can occur during the operation of the I2 task. |                                                                                                                                                                               |

| Functions   | <b>F</b>                                                                                   | 1                                                                                                                                                                             |

|             | Function                                                                                   | init                                                                                                                                                                          |

|             | Description                                                                                | I2S initialization event callback.<br>The I2S component will call this when it first initializes on first<br>run of after a restart.                                          |

|             | Туре                                                                                       | <pre>void init(i2s_config_t &amp; ?i2s_config,</pre>                                                                                                                          |

|             | Parameters                                                                                 | i2s_config<br>This structure is provided if the connected com-<br>ponent drives an I2S bus. The members of the<br>structure should be set to the required configura-<br>tion. |

|             |                                                                                            | tdm_config<br>This structure is provided if the connected com-<br>ponent drives an TDM bus. The members of the<br>structure should be set to the required configura-<br>tion. |

|             | Function                                                                                   | restart_check                                                                                                                                                                 |

|             | Description                                                                                | I2S restart check callback.<br>This callback is called once per frame. The application must<br>return the required restart behaviour.                                         |

|             | Туре                                                                                       | <pre>i2s_restart_t restart_check()</pre>                                                                                                                                      |

|             | Returns                                                                                    | The return value should be set to I2S_NO_RESTART, I2S_RESTART or I2S_SHUTDOWN.                                                                                                |

Continued on next page

| Function           | receive                                                                                                                                                                                   |  |  |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Description        | Receive an incoming sample.<br>This callback will be called when a new sample is read in by the<br>I2S component.<br>void receive(size_t index, int32_t sample)                           |  |  |

| Туре               |                                                                                                                                                                                           |  |  |

| Parameters         | index The index of the sample in the frame.                                                                                                                                               |  |  |

|                    | sample The sample data as a signed 32-bit value. The component may not use all 32 bits of the value (for example, many I2S codecs are 24-bit), in which case the bottom bits are ignored. |  |  |

| Function           | send                                                                                                                                                                                      |  |  |

| Description        | Request an outgoing sample.<br>This callback will be called when the I2S component needs<br>new sample.                                                                                   |  |  |

|                    | <pre>int32_t send(size_t index)</pre>                                                                                                                                                     |  |  |

| Туре               | <pre>int32_t send(size_t index)</pre>                                                                                                                                                     |  |  |

| Type<br>Parameters | <pre>int32_t send(size_t index) index The index of the requested sample in the frame.</pre>                                                                                               |  |  |

# 3.5 The I<sup>2</sup>S frame-based callback interface

| Туре        | i2s_frame_callback_if                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Description | Interface representing callback events that can occur during the operation of the I2S task.<br>This is specific to the frame-based I2S master task which uses hardware generation of BCLK and transfers samples as arrays rather than individual channels, resulting in much less senesitivity to back pressure in the send/recieve cases. This interface is supported on xCORE200 processors only. |                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Functions   | Function                                                                                                                                                                                                                                                                                                                                                                                            | init                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|             | Description                                                                                                                                                                                                                                                                                                                                                                                         | I2S frame-based initialization event callback.<br>The I2S component will call this when it first initializes on first<br>run of after a restart.                                                                                                                                                                                                                                   |  |  |  |  |

|             | Туре                                                                                                                                                                                                                                                                                                                                                                                                | <pre>void init(i2s_config_t &amp; ?i2s_config,</pre>                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|             | Parameters                                                                                                                                                                                                                                                                                                                                                                                          | <pre>i2s_config<br/>This structure is provided if the connected com-<br/>ponent drives an I2S bus. The members of the<br/>structure should be set to the required configura-<br/>tion.<br/>tdm_config<br/>This structure is provided if the connected com-<br/>ponent drives an TDM bus. The members of the<br/>structure should be set to the required configura-<br/>tion.</pre> |  |  |  |  |

|             |                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|             | Function<br>Description                                                                                                                                                                                                                                                                                                                                                                             | restart_check<br>I2S frame-based restart check callback.<br>This callback is called once per frame. The application must<br>return the required restart behaviour.                                                                                                                                                                                                                 |  |  |  |  |

|             | Туре                                                                                                                                                                                                                                                                                                                                                                                                | <pre>i2s_restart_t restart_check()</pre>                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |